QR code

Products

Nobis loquere

Fax

+86-579-87223657

E-mail

Oratio

Wangda Road, Ziyang Street, Wuyi Comitatus, Jinhua urbs, Zhejiang Provincia, China

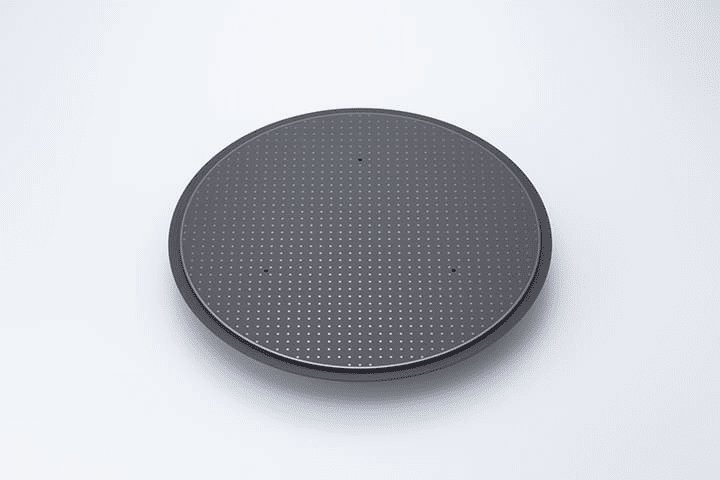

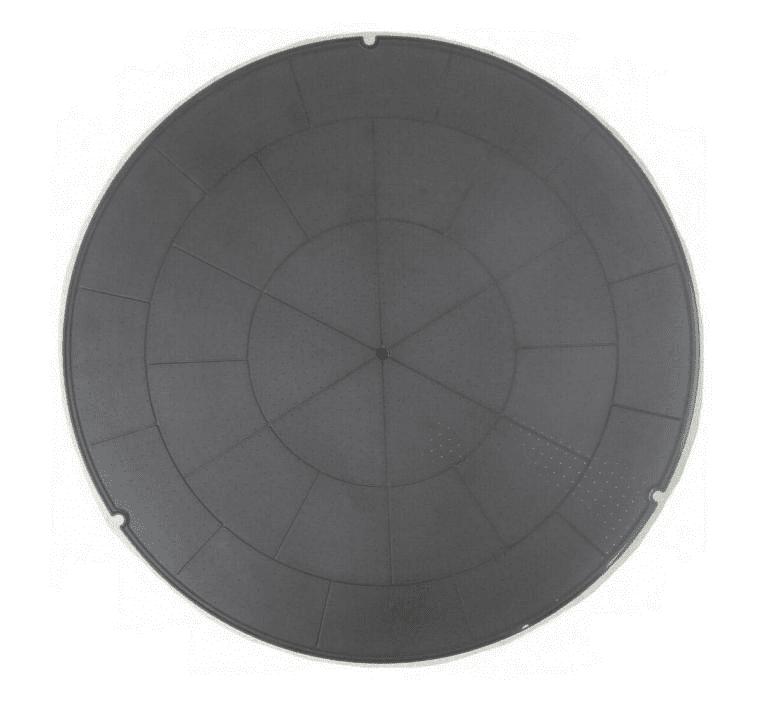

Electrostatic Chuck (Esc pro brevi) est a fabrica quod usus electrostatic vis ad absorbet et fixSilicon Wafersvelalias subiecta. Est late in Plasma Etching (Plasma Etching), eget vapor depositione (CVD), physica vapor depositione (PVD) et alia processus links in vacuo environment of semiconductor vestibulum.

Comparari cum traditional mechanica fixtures, ESC potest firmiter fix wafers sine mechanica accentus et pollutio, amplio processus accurate et constantia, et est unus ex key apparatu components of altus-praecision semiconductor processibus.

Electrostatic chucks potest dividitur in sequentibus genera secundum structural consilio, electrode materiae et adsorption modos:

I. Monopolar ESC

Structura: Unus Electrode iacuit + unum terram planum

Features: postulat auxiliaris Helium (ipse) et NITROGENIUM (n₂) ut in insulating medium

Applicationem: idoneam ad processui summus impeditance materiae ut sio₂ et si₃n₄

II. Bipolar ESC

Structuram: duo electrodes, positivum et negans electrodes sunt embedded in Ceramic vel polymer iacuit respectively

Features: Non potest operari sine additional instrumentis et idoneam ad materiae cum bona conductivity

Commoda: fortior adsorption et citius responsum

III. Thermal Imperium (se Tergum Refrigerant Esc)

Function: combined cum a tergo refrigerationem ratio (plerumque helium), temperatus est pressius imperium dum fixing in lagae

Application: late in plasma etching et processibus ubi etching profundum necessitates ad esse pressius imperium

4. Ceramic ESCMaterial:

High Nulla Ceramic materiae ut aluminium cadmiae (Alo₃₃) Aluminium Nitride (Aln) et Silicon Nitride (si₃n₄) solent usus est.

Features: ROSIO resistentia, optimum insulsio perficientur et excelsum scelerisque conductivity.

I. PLASMA etching ESC fixes et laganum in reactionem thalamum et realizes retro refrigerationem, moderando in laganum temperatus intra ± I ℃, ita ense ut etching rate uniformitatem (CD uniformitatem), quod in ECRUS rate uniformitatem (CD uniformitas), quod in III%.

II. Eget vapor depositione (cvd) ESC potest consequi firmum adsorption de wafers sub altum temperatus conditionibus, efficaciter supprimere deformatio, et amplio et adhaesionem tenui film depositione.

III. Physica vapor depositione (PVD) ESC praebet contontless solidamentum ne lagrae damnum fecit per mechanica accentus, et praecipue idoneam ad processui de ultra-tenuis lagana (<150μm).

IV. Ion implantationthe temperatus temperatus imperium et firmum clamping capabilities of ESC ne loci damnum ad laganum superficiem debitum ad crimen cumulationem, cursus accurate implantationis dose potestate.

V. Advanced Packagingin chiplets et 3D IC packaging, Esc est etiam in redistribeudo laminis (RDL) et laser Processing, supporting processus non-vexillum lagam magnitudinum.

I. Tenens Force DegradationProbem Descriptio:

Post longa-term operatio, ex electrode senescit aut tellus superficiem contagione, in ESC tenet Force decrescit, causando laganum ut subcinctus vel cadunt off.

SOLUTIO Usus Pure Purgato et iusto superficies curatio.

II. Electrostatic missionem (ESD) periculum:

High voltage bias ut faciam instantanea defluxiones, damaging laganum vel apparatu.

Countermeasures: Design a multi-iacuit Electrode Nulla structuram et configurare ESD suppressio circuitu.

III. Temperature non-uniformitas ratio:

Sive refrigerationem terga Esc vel differentia in scelerisque conductivity Ceramics.

Data: Semel temperatus deviationem excedit ± II ℃, ut faciam anching profundum deviation of> ± X%.

SOLUTIO: Ceramics Ceramics Ceramal (ut aln) cum summus pressura imperium ratio (0-15 Torr).

IV. Depositionem contaminyproblem:

Processus residua (ut cf₄, sih₄ decomposition products) deposita super superficiem ESC, afficiens adsorption facultatem.

Countermeasure: Use Plasma in -u elit Purgato technology et praestare exercitatione Purgato post currit 1,000 wafers.

User focus

Necessitates ipsam

Commendatur solutions

Wafer fixation reliability

Ne Wafer Slippage vel PERFLUO per summus temperatus processibus

Usus Bipolar ESC

Temperatus imperium accuracy

Die I ° C ad processum stabilitatem

Thermally regitur ESC, cum refrigerationem ratio

Corrosion resistentia et vitae

Stabilis usus undER summus density Plasma processes> (V) h

Ceramic ESC (Aln / Alico₃)

Velox responsio et sustentationem commodum

Velox Clamping Release, Securus Purgato et sustentationem

Dedakable ESC structura

Wafer Type Compatibility

Subsidiis CC mm / CCC mm / non-circularis lectus processus

MODULAR ESC Design

+86-579-87223657

Wangda Road, Ziyang Street, Wuyi Comitatus, Jinhua urbs, Zhejiang Provincia, China

Copyright © 2024 WuYi TianYao Advanced Material Tech.Co.,Ltd. All Rights Reserved.

Links | Sitemap | RSS | XML | Privacy Policy |