QR code

Products

Nobis loquere

Fax

+86-579-87223657

E-mail

Oratio

Wangda Road, Ziyang Street, Wuyi Comitatus, Jinhua urbs, Zhejiang Provincia, China

Vestibulum singulis semiconductor productum postulat centum processibus et tota vestibulum processus dividitur in octo gradibus:Wafer processui - oxidatio - Photolithogy - etching - Tenues film deposition - internitio - probatio - packaging.

![]()

Gradus I:Wafer processui

Omnes semiconductor processus satus cum grano harenae! Quia Silicon continebat in harenae est rudis materia opus ad producendum wafers. Tafers sunt per crustae interficiam de uno crystallum cylindricos factum de Silicon (si) aut Gallii Arsenide (Gaas). Ut eliciunt summus puritas Silicon materiae, silica harenae, specialis materia cum Silicon dioxide contentus de usque ad XCV%, quod opus est, quae est etiam pelagus rudis materia pro wafers. Wafer processui est processus faciendi super tafers.

Ingot casting

Primo, quod harenae necessitates ut succenderetur ad separare carbonis Monoxide et Silicon in ea et processus repetitur donec ultra-excelsum puritatem electronic gradu Silicon (eg, si) est adeptus. High-puritatem Silicon dissolvit in liquidam et cucurrit in unum crystallum solidam formam, vocavit est "Ingot", quod est primus gradus in semiconductor vestibulum.

In vestibulum praecisione Silicon ingots (Silicon columnas) valde altum, perveniens Nanometer campester et late usus vestibulum modum est czochralski modum.

Ingot secans

Post priorem gradum perficitur necessarium interficiam duos fines ingot cum adamantino vidit et interficiam eam tenues crustae quadam crassitudine. Diameter in ingot SLACENTUM determinat magnitudinem laganum. Maior et tenuior lagana potest dividitur in magis utilis unitates, quod adjuvat ad redigendum productio costs. Post cutting Silicon Ingot, necesse est addere "plana area" vel "dent" marcas in crustae ad faciliorem occasum processui direction ut a vexillum in subsequentibus gradibus processui direction ut a vexillum in subsequentibus gradibus.

Wafer Superficiem Polishing

In crites adeptus per quod supra secans processus dicuntur "nuda wafers", id est, unprocessed "rudis wafers". Superficies nudum laganum inaequaliter et circuitus exemplar non typis directe. Ergo necesse est primo removere superficiem defectibus per molere et eget etching processibus, deinde Poloniae formare lenis et removere RELICTUM contaminants per Purgato obtinere complevit laganum mundum.

Gradus II: oxidatio

Partes oxidationis processus est formare tutela amet super superficiem lagae. Protegit laganum a chemical impudicitiis, prohibet leakage current ab intrantes in circuitu, impedit diffusio per ion implantationem, et prohibet laganum a labore per etching.

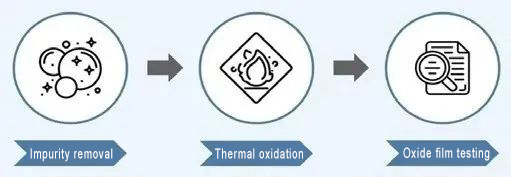

Primum gradum in oxidation processus est removere impudicitiis et contaminantium. Removere requirit quatuor gradus ad removendum organicum materia, metallum impudicitiis et evaporate RELICTUM aqua. After cleaning, the wafer can be placed in a high temperature environment of 800 to 1200 degrees Celsius, and a silicon dioxide (i.e. "oxide") layer is formed by the flow of oxygen or steam on the surface of the wafer. Oxygeni diffuses per cadmiae accumsan et reagit cum Silicon ad formare cadmiae layer varianim crassitudine et crassitudo potest metiri post oxidatio perficitur.

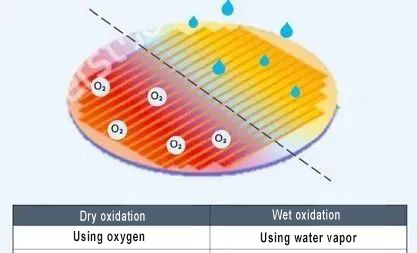

Oxidants et oxidation oxidants oxidation fretus oxidants in oxidation reactionem, oxidatio oxidation processus in aridam oxidatio et infectum oxidatio. Prior usus pura oxygeni ad producendum Silicon dioxide iacuit, quod tardus sed cadmiae layer tenuis et densa. Haec postulat tam oxygeni et altus solutum aqua vapor, quod propria est ieiunium incrementum rate sed relative densissima tutela iacuit cum humili densitate.

In addition ad oxidant, sunt alia variables quod afficiunt crassitudine Silicon dioxide iacuit. Primo, in laganum structuram, eius superficiem defectibus et internum doping concentration erit afficiunt rate of cadmiae iacuit generationem. In addition, superior pressura et temperatus generatae per oxidatio apparatu, quod citius in cadmiae layer et generatur. Per oxidatio processus, necesse est uti phantasma sheet secundum positionem laganum in unitatis praesidio lagam et reducere differentia in oxidatio gradu.

Gradus III: Photolithography

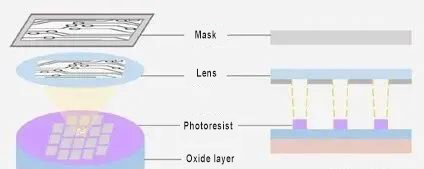

Photolithogsography est "print" in circuitu exemplar onto laganum per lucem. Non possumus intelligere quod drawing planum map requiratur ad semiconductor vestibulum super superficiem in laganum. Superioris ad cuneum exemplar ad altiorem integrationem perfectis chip, quod effectum per Advanced Photolithography technology. In specie, photolithography potest dividitur in tres gradus: coating photoresist, nuditate et development.

Coating

Primum gradum tractus a circuitu in laganum est tunica photoresist in cadmiae iacuit. Photoresist facit laganum a "photo paper" per chemical proprietatibus mutantur. Et tenuior de photoresist accumsan super superficiem laganum, magis uniformis et coating, et pulcherrima exemplar quod potest typis. Hoc gradum potest fieri per "nent coating" modum. Secundum differentiam in lucem (ultraviolet) Reactivity, photoresists potest dividitur in duo genera: positivum et negativum. Prior et decomposi evanescet post nuditate lucem relinquens exemplar incolumis area dum vero polymerize post nuditate lucem et exemplar expositae partis appareat.

Expositio

Post photoresist amet tegitur lagam, circuitus excudendi potest compleri potest a lumen nuditate. Hoc processus dicitur "nuditate". Non possumus selectas transire lux per detectio apparatu. Cum lumen transit per persona continet circuitus exemplar, in circuitu potest typis in lagam iactaret photoresist film infra.

Per patefacio processus, et pulcherrimi exemplaria, magis components ad ultima chip potest accommodare, quod adjuvat ad amplio productio efficientiam et redigendum sumptus cuiusque pars. In hoc agro, novi technology quod est currently attrahentis multa operam est EUV lithography. Lam investigationis coetus habet communiter developed novum arida film photoresist technology cum opportuna sociis Asml et IMEC. Hoc technology potest vehementer amplio productivity et cedat de EUV lithography expositionis processus per meliorem resolutionem (a key factor in fine-tuning circuitus latitudine).

Progressio

In gradum post nuditate est ad imbre in elit in laganum, ad removere photoresist in nudato area exemplar, ut typis circuitu exemplaris revelanda. Postquam progressionem perficitur necessitates sedatus variis mensurae apparatu et optical microscopi ut qualis est circuita tabula.

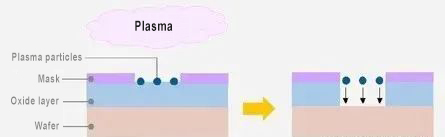

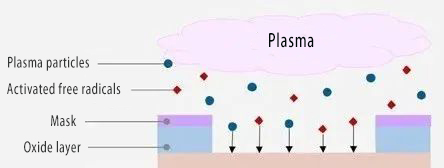

Gradus IV: Etching

Post photographyography de Circuit Diagram perficitur in laganum, anching processus est ad removendum ullam excess cadmiae film et relinquere solum semiconductor circuitu tabula. Ad hoc, liquidum, Gas aut Plasma adhibetur ad removendum electus excess partes. Sunt duo principalis modi etching, fretus in substantiis solebat: infectum etching per specifica eget solution ad chemica reflecti ad removendum a cadmiae, et siccis etching per Gas vel Plasma.

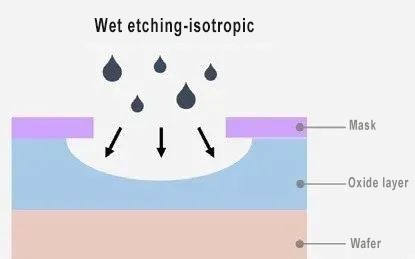

Infectum etching

Usus Etching usura eget solutions ut aufero cadmiae films habet commoda humilis sumptus, ieiunium etching celeritate et altum productivity. Sed infectum etching isotropic, id est ejus celeritate est idem in aliquo directionem. Hoc facit in persona (vel sensitivo film), ut non sit omnino varius cum et safched cadmiae film, sic difficile ad aliquid valde denique Circuit Diagrams.

Arida etching

Siccis etching dividitur in tres genera. Primum est eget etching, qui utitur etching vapores (maxime hydrogenium fluoride). Sicut infectum etching, hoc modus est isotropic, quod significat non idoneam ad denique etching.

Secundum modum est corporis spundat, quod utitur ions in Plasma ad impulsum et removere excessus cadmiae layer. Sicut anisotropic etching modum, spundly etching habet diversas etching rates in horizontali et verticali directiones, ita et melior quam eget etching. Tamen incommodum est modus est quod etching celeritate tardus quia innititur omnino in corporalis reactionem fecit per ionam collisio.

Ultima tertia ratio est reactive Ion etching (Rie). Rie combines primi duo modi, id est, dum usura Plasma pro ionization corporalis etching, eget etching est cum auxilio liberi radicalis generatae post Plasma activation. In addition ut etching celeritate excedens primum duo modi, rie potest uti anisotropic characteres of ions ad consequi summus praecisione exemplar etching.

Hodie, arida etching est late ad amplio cede de fine semiconductor circuits. Suscipio plena-lagae etching uniformitatem et augendae etching celeritate sunt critica, et hodie maxime provectus arida etching apparatu est supporting productio ex maxime provectus logica et memoriam eu cum altiorem perficientur.

Vetek semiconductor est professional Chinese ManufacturerTantalum carbide coating, Silicon carbide coating, Special Graphite, Silicon Carbide CeramicsetAlii Semiconductor Ceramics. Vetek Semiconductor est committitur providing provectus solutions pro variis sic wafer products pro semiconductor industria.

Si vos es interested in super products, placere sentire liberum contactus nos directe.

Vulgus: + 86-180 (VI) CMXXII DCCLII

Whatsapp: CLXXX CLXXX (VI) CMXXII DCCLII

Email: Anny@veteksemi.com

+86-579-87223657

Wangda Road, Ziyang Street, Wuyi Comitatus, Jinhua urbs, Zhejiang Provincia, China

Copyright © 2024 WuYi TianYao Advanced Material Tech.Co.,Ltd. All Rights Reserved.

Links | Sitemap | RSS | XML | Privacy Policy |